MASTERTHESIS Niels Gandraß

# A Uniform API for Cross-Platform Timer Hardware Abstraction on Resource Constrained IoT Devices

FAKULTÄT TECHNIK UND INFORMATIK Department Informatik

Faculty of Computer Science and Engineering Department Computer Science

HOCHSCHULE FÜR ANGEWANDTE WISSENSCHAFTEN HAMBURG Hamburg University of Applied Sciences Niels Gandraß

# A Uniform API for Cross-Platform Timer Hardware Abstraction on Resource Constrained IoT Devices

Masterarbeit eingereicht im Rahmen der Masterprüfung im Studiengang *Master of Science Informatik* am Department Informatik der Fakultät Technik und Informatik der Hochschule für Angewandte Wissenschaften Hamburg

Betreuender Prüfer: Prof. Dr. Thomas C. Schmidt Zweitgutachter: Prof. Dr. Franz Korf

Eingereicht am: 23. Februar 2022

### Niels Gandraß

#### Thema der Arbeit

A Uniform API for Cross-Platform Timer Hardware Abstraction on Resource Constrained IoT Devices

#### Stichworte

Betriebssysteme, Eingebettete Systeme, Hardwareabstraktion, Hardware Timer, Ressourcenbeschränkte Geräte, Softwaredesign

#### Kurzzusammenfassung

Timer sind Bestandteil jedes Mikrocontrollers und beeinflussen zahlreiche Aspekte eingebetteter Systeme. Ihre wachsende Vielfalt lässt sich jedoch nur noch unzureichend über die historisch gewachsenen APIs eingebetteter Betriebssysteme abbilden. Ein solider und zukunftsorientierter Ersatz für die aktuelle Hardware-Abstraktion ist daher notwendig.

Diese Arbeit bietet einen umfassenden Einblick in heutige Timer-Peripherie. Wir analysieren die Timer von 43 Gerätefamilien und acht Herstellern, charakterisieren Timeouts für typische IoT Anwendungen, beleuchten die Timer APIs eingebetteter Betriebssysteme, identifizieren Mängel aktueller Lösungen und diskutieren Ansätze zur Hardware-Abstraktion. Auf dieser Wissensbasis entwickeln wir ein zweischichtiges Low-level Timer API Design und implementieren es für das RIOT Betriebssystem. *uTimer* ermöglicht die transparente Nutzung unterschiedlicher Timer-Typen über eine gemeinsame Schnittstelle. Diese ist plattformunabhängig nutzbar und stellt grundlegende sowie gerätespezifische Funktionen zur Verfügung. Timer und Kanäle werden im Durchschnitt verdreifacht und neue Timer-Typen, wie beispielsweise *ultra low-power timer*, nativ unterstützt. Die Vereinheitlichung aktueller APIs sorgt darüber hinaus für konsistenten und gut wartbaren Timer-Code innerhalb des gesamten RIOT-Ökosystems.

Wir entwickeln plattformunabhängige Unit-Tests sowie Benchmarks und führen diese auf insgesamt 14 Mikrocontrollern in einem HiL-Testbett mit CI Unterstützung aus. Die vorgestellte *uTimer* API benötigt für ihre zusätzliche Abstraktion lediglich zwischen 6 und 21 CPU-Zyklen. Dies entspricht einem Timeout-Fehler von weniger als 0.05%. Diesem steht die Nutzbarkeit zahlreicher neuer Timer-Funktionen gegenüber. Verzichtet man für spezielle Anwendungsfälle auf die Abstraktion von Timer-Typen, so kann jeglicher API-Overhead vollständig vermieden werden. Die automatisierte Ausführung von Tests und Benchmarks auf der aktuellen Code-Basis sowie für alle bevorstehenden Änderungen erleichtert außerdem die Entwicklung nachhaltiger Peripherie-Treiber und ermöglicht deren fundierte Bewertung.

## Niels Gandraß

### Title of Thesis

A Uniform API for Cross-Platform Timer Hardware Abstraction on Resource Constrained IoT Devices

#### Keywords

embedded systems, hardware abstraction, hardware timers, operating systems, resource constrained devices, software design

### Abstract

Timers are part of every microcontroller and influence numerous aspects of embedded applications. As the heterogeneous spectrum of timer peripherals continues to grow, embedded OSs increasingly struggle to expose novel timers and advanced features via their time-honoured APIs. The need for comprehensive and future-proof hardware abstraction therefore arises.

This work provides detailed insight into modern timer peripherals. We conduct a survey of timer hardware across 43 device families from eight manufacturers, characterize typical timeouts within IoT applications, examine timer APIs of popular embedded OSs, identify deficiencies of current solutions, and discuss different approaches to hardware abstraction. This forms a solid base, on which a two-layered low-level timer API design is proposed and implemented for the RIOT OS. Its uniform interface allows transparently interchangeable use of all hardware timers. Generic and peripheral-specific features are exposed, yet application portability is preserved. On average, available timers and channels are tripled, and previously unexposed advanced timer types such as ultra-low power timers become usable. Current interfaces are streamlined to form a single API, fostering uniformity and maintainability of timer code throughout the whole RIOT ecosystem.

We develop platform-independent timer unit tests and benchmark suites that are executed using a HiL testbed with CI support. The performance of our novel uTimer API is assessed on 14 MCUs. It only adds between six and 21 CPU cycles of abstraction overhead compared to existing solutions. This corresponds to timeout errors of less than 0.05% while numerous modern timer features are made available to user applications and high-level OS modules. For high-performance use, deliberate renunciation of timer-type transparency eliminates any performance differences between APIs at the cost of narrowing application portability. Automated execution of the contributed unit tests and benchmarks on nightly builds and pull requests moreover facilitates the development of sustainable implementations and permits their sound evaluation.

# Contents

| Li            | st of | Figur  | es                                        | ix   |

|---------------|-------|--------|-------------------------------------------|------|

| $\mathbf{Li}$ | st of | Table  | s                                         | x    |

| $\mathbf{Li}$ | st of | Acron  | iyms                                      | xi   |

| $\mathbf{Li}$ | st of | Symb   | ols                                       | xiv  |

| $\mathbf{Li}$ | st of | Listin | gs                                        | xv   |

| 1             | Intr  | oduct  | ion                                       | 1    |

| <b>2</b>      | Bac   | kgrou  | nd                                        | 3    |

|               | 2.1   | Micro  | controllers and Timer Peripherals         | . 3  |

|               | 2.2   | Hardv  | vare Abstraction Techniques               | . 4  |

|               | 2.3   | Embe   | dded Operating Systems                    | . 6  |

| 3             | Pro   | blem S | Statement                                 | 7    |

|               | 3.1   | Limits | s of Platform-specific Solutions          | . 7  |

|               | 3.2   | The A  | bstraction Trade-off                      | . 8  |

|               | 3.3   | Hardv  | vare Heterogeneity                        | . 9  |

|               | 3.4   | Valida | ation and Optimization                    | . 10 |

| <b>4</b>      | Ana   | alysis |                                           | 11   |

|               | 4.1   | Relate | ed Work                                   | . 11 |

|               |       | 4.1.1  | Properties of Hardware Timers             | . 11 |

|               |       | 4.1.2  | Comparative Analyses of Timer Peripherals | . 12 |

|               |       | 4.1.3  | Hardware Abstraction and Timer Interfaces | . 13 |

|               |       | 4.1.4  | Embedded Operating Systems                | . 14 |

|               |       | 4.1.5  | Miscellaneous                             | . 17 |

|               |       | 4.1.6  | Summary                                   | . 17 |

|               | 4.2   | RIOT   | OS Timer Modules                          | . 18 |

|               |       | 4.2.1  | General-purpose Timer Driver              | . 18 |

|               |       | 4.2.2  | Real-time Clock Driver                    | . 20 |

|   |     | 4.2.3<br>4.2.4 | Real-time Timer Driver20Pulse-width Modulation Driver20 |

|---|-----|----------------|---------------------------------------------------------|

|   |     | 4.2.4<br>4.2.5 | Watchdog Timer Driver   21                              |

|   |     | 4.2.5<br>4.2.6 |                                                         |

|   |     | 4.2.0<br>4.2.7 | 5 ·                                                     |

|   | 4.3 |                | 5                                                       |

|   | 4.3 | пагам<br>4.3.1 | 1 0                                                     |

|   |     | -              | •                                                       |

|   |     | 4.3.2<br>4.3.3 | Methodology                                             |

|   |     |                | Results   25     Outstand line Table and Lenge   22     |

|   |     | 4.3.4          | Outstanding Tasks and Issues                            |

|   |     | 4.3.5          | Summary                                                 |

|   | 4.4 |                | ase Analysis                                            |

|   |     | 4.4.1          | Timeouts within RIOT OS Modules and Drivers             |

|   |     | 4.4.2          | Network Protocol Timing Requirements                    |

|   |     | 4.4.3          | Summary                                                 |

| 5 | Des | ign of         | a Uniform Low-level Timer API 38                        |

| Č | 5.1 | 0              | and s and Goals                                         |

|   | 0.1 | 5.1.1          | Features and Usability                                  |

|   |     | 5.1.2          | Peripheral State and Capabilities                       |

|   |     | 5.1.3          | Application Portability                                 |

|   |     | 5.1.4          | Configuration Management                                |

|   |     | 5.1.5          | System Impact and Resources                             |

|   |     | 5.1.6          | Miscellaneous                                           |

|   | 5.2 |                | 1                                                       |

|   | 0   | 5.2.1          | Overview                                                |

|   |     | 5.2.2          | Timer Types and Instances                               |

|   |     | 5.2.3          | Hardware-facing API                                     |

|   |     | 5.2.4          | User-facing API                                         |

|   |     | 5.2.5          | Interrupt Handling                                      |

|   |     | 5.2.6          | Configuration Management                                |

|   |     | 5.2.7          | Application Portability   52                            |

|   | 5.3 |                | Examples                                                |

|   | 5.4 | ~              | 54                                                      |

|   |     | 5.4.1          | Design Trade-offs                                       |

|   |     | 5.4.2          | Issues                                                  |

|   |     | 0.1.2          | 00                                                      |

| 6 | Imp | olemen         | tation 57                                               |

|   | 6.1 | RIOT           | System Architecture                                     |

|   | 6.2 | Low-le | evel Timer Module                                                                                                         |

|---|-----|--------|---------------------------------------------------------------------------------------------------------------------------|

|   |     | 6.2.1  | Compile-time Configuration Management                                                                                     |

|   |     | 6.2.2  | Datatype Definitions and Defaults                                                                                         |

|   |     | 6.2.3  | Hardware-facing API                                                                                                       |

|   |     | 6.2.4  | User-facing API                                                                                                           |

|   | 6.3 | Platfo | rm Implementations                                                                                                        |

|   |     | 6.3.1  | Atmel / Microchip ATmega AVR    64                                                                                        |

|   |     | 6.3.2  | Espressif ESP8266 and ESP32 64                                                                                            |

|   |     | 6.3.3  | Silicon Labs EFM32                                                                                                        |

|   |     | 6.3.4  | STMicroelectronics STM32 65                                                                                               |

|   |     | 6.3.5  | Texas Instruments MSP430                                                                                                  |

|   | 6.4 | Valida | $ation \dots \dots$ |

| 7 | Eva | luatio | n 69                                                                                                                      |

|   | 7.1 | Conce  |                                                                                                                           |

|   |     | 7.1.1  | Hardware in the Loop                                                                                                      |

|   |     | 7.1.2  | Primitive Hardware in the Loop Integration Product                                                                        |

|   |     | 7.1.3  | Robot Framework                                                                                                           |

|   | 7.2 | Metho  | odology                                                                                                                   |

|   | 7.3 | Test S | Setup                                                                                                                     |

|   |     | 7.3.1  | Architecture                                                                                                              |

|   |     | 7.3.2  | Accuracy and Hardware Limits                                                                                              |

|   |     | 7.3.3  | Measurement Stability                                                                                                     |

|   |     | 7.3.4  | Continuous Integration and Benchmark Automation                                                                           |

|   | 7.4 | Bench  | marks                                                                                                                     |

|   |     | 7.4.1  | GPIO Overhead                                                                                                             |

|   |     | 7.4.2  | Basic Timer Operations                                                                                                    |

|   |     | 7.4.3  | Timeouts                                                                                                                  |

|   |     | 7.4.4  | Interrupt Handling                                                                                                        |

|   |     | 7.4.5  | Abstraction Overhead                                                                                                      |

|   | 7.5 | Discus | ssion $\ldots \ldots $  |

|   |     | 7.5.1  | API Performance    92                                                                                                     |

|   |     | 7.5.2  | Abstraction Trade-off                                                                                                     |

|   |     | 7.5.3  | Binary Size and Memory Usage                                                                                              |

|   |     | 7.5.4  | Peripheral Availability                                                                                                   |

|   |     | 7.5.5  | Virtual Timer Drivers                                                                                                     |

|   |     | 7.5.6  | Code Quality and Usability                                                                                                |

|   |     | 7.5.7  | Automation                                                                                                                |

|   |     | 7.5.8  | Integration                                                                                                               |

|   |     | 7.5.9  | Issues                                                                                                                    |

| 8                              | Cor              | clusior | and Outlook                                                    | 101 |  |  |  |

|--------------------------------|------------------|---------|----------------------------------------------------------------|-----|--|--|--|

|                                | 8.1              | Future  | Work                                                           | 102 |  |  |  |

| Bi                             | Bibliography 103 |         |                                                                |     |  |  |  |

| $\mathbf{A}$                   | Har              | dware   | Analysis Results                                               | 108 |  |  |  |

|                                | A.1              | Colum   | n Key for Analysis Criteria                                    | 108 |  |  |  |

|                                |                  | A.1.1   | Timer Type                                                     | 108 |  |  |  |

|                                |                  | A.1.2   | Counter Width                                                  | 108 |  |  |  |

|                                |                  | A.1.3   | Compare Channels                                               | 108 |  |  |  |

|                                |                  | A.1.4   | Prescaler Type                                                 | 109 |  |  |  |

|                                |                  | A.1.5   | Max Prescaler                                                  | 109 |  |  |  |

|                                |                  | A.1.6   | Chaining Support                                               | 109 |  |  |  |

|                                |                  | A.1.7   | Compare INT                                                    | 109 |  |  |  |

|                                |                  | A.1.8   | Overflow INT                                                   | 110 |  |  |  |

|                                |                  | A.1.9   | Event Flags                                                    | 110 |  |  |  |

|                                |                  | A.1.10  | Auto-reload                                                    | 110 |  |  |  |

|                                |                  | A.1.11  | PWM Generation                                                 | 110 |  |  |  |

|                                |                  | A.1.12  | Internal CLKs                                                  | 111 |  |  |  |

|                                |                  | A.1.13  | External CLKs                                                  | 111 |  |  |  |

|                                |                  | A.1.14  | Low-power CLK                                                  | 111 |  |  |  |

|                                |                  | A.1.15  | Deep-sleep Active                                              | 112 |  |  |  |

|                                |                  | A.1.16  | Unresolved or Not-applicable Items                             | 112 |  |  |  |

|                                | A.2              | Timer   | Comparison Matrices (TCMs)                                     | 113 |  |  |  |

| в                              | uTi              | mer Al  | PI Definition                                                  | 121 |  |  |  |

|                                | B.1              | Type I  | Definitions                                                    | 121 |  |  |  |

|                                | B.2              | Hardw   | are-facing API                                                 | 126 |  |  |  |

|                                | B.3              | User-fa | acing API                                                      | 131 |  |  |  |

|                                |                  | B.3.1   | $Peripheral Management \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 131 |  |  |  |

|                                |                  | B.3.2   | Basic Timer Functions                                          | 132 |  |  |  |

|                                |                  | B.3.3   | Compare Channels and Timeouts                                  | 133 |  |  |  |

|                                |                  | B.3.4   | Dynamic Property Interface                                     | 136 |  |  |  |

|                                |                  | B.3.5   | Convenience Functions                                          | 137 |  |  |  |

| Glossary 138                   |                  |         |                                                                |     |  |  |  |

| Selbstständigkeitserklärung 14 |                  |         |                                                                |     |  |  |  |

# List of Figures

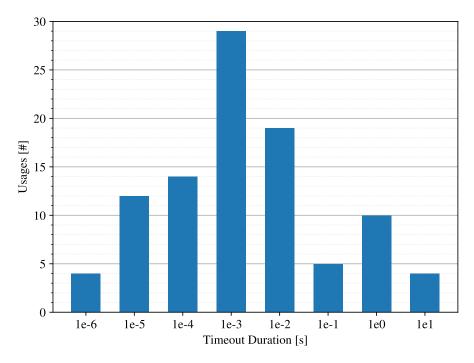

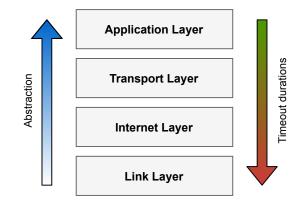

| 2.1<br>2.2   | Core components of a basic hardware timer                                                                                       | $\frac{4}{5}$ |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|---------------|

| $4.1 \\ 4.2$ | Distribution of shortest timeouts used within RIOT OS modules and drivers<br>Overview of the RFC 1122 communication layer model | 35<br>36      |

| 1.2          |                                                                                                                                 | 50            |

| 5.1          | Overview of the proposed low-level timer API design                                                                             | 43            |

| 5.2          | hAPI driver design concepts for code reusability                                                                                | 46            |

| 5.3          | A virtual hAPI driver used for timer chaining                                                                                   | 47            |

| 5.4          | Exemplary uAPI compound function                                                                                                | 49            |

| 5.5          | Interactive selection of timer peripherals using Kconfig                                                                        | 51            |

| 6.1          | Structural overview of RIOT                                                                                                     | 58            |

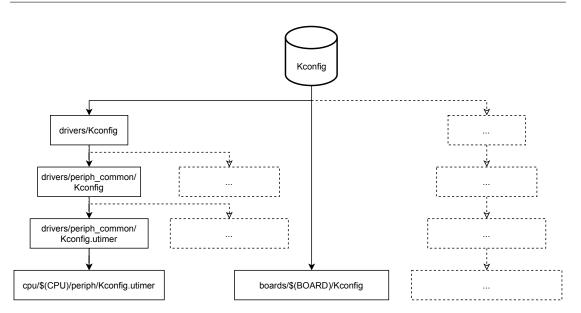

| 6.2          | Hierarchical structure of the Kconfig definition files                                                                          | 60            |

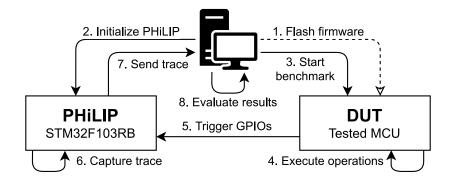

| 7.1          | Architecture of our benchmark setup                                                                                             | 73            |

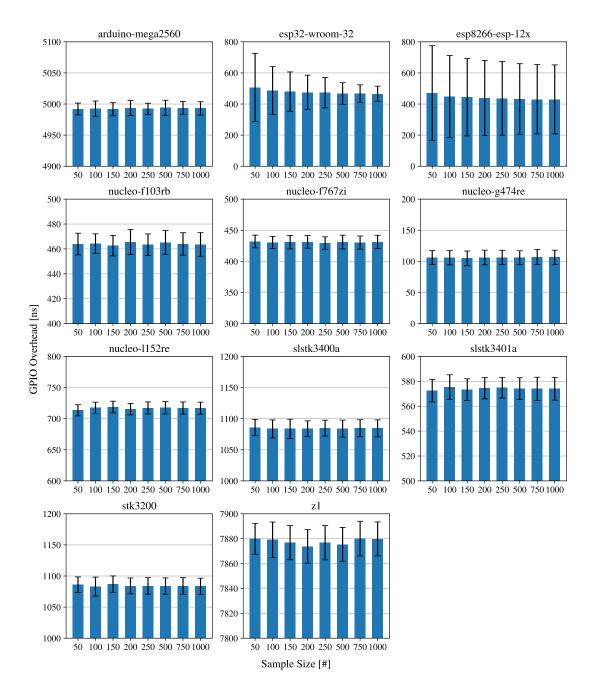

| 7.2          | Comparison of GPIO overhead on all boards using different sample sizes                                                          | 75            |

| 7.3          | A single rack from the HiL testbed of the RIOT community                                                                        | 77            |

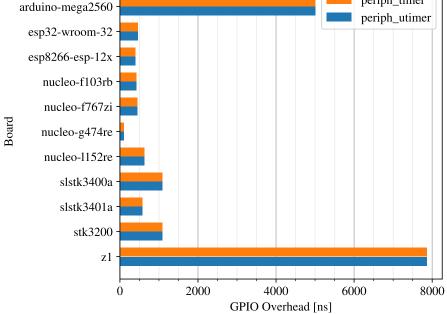

| 7.4          | Definition of the GPIO overhead benchmark                                                                                       | 78            |

| 7.5          | GPIO overhead for all boards within our CI setup                                                                                | 78            |

| 7.6          | Definition of the timer base operation benchmark                                                                                | 79            |

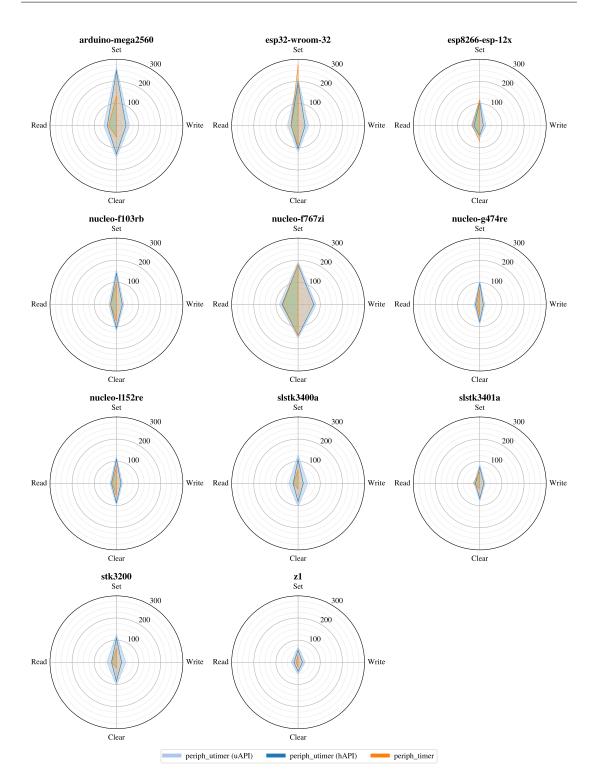

| 7.7          | CPU cycles consumed by read, write, set, and clear operations                                                                   | 80            |

| 7.8          | Definition of the one-shot timeout latency benchmark                                                                            | 83            |

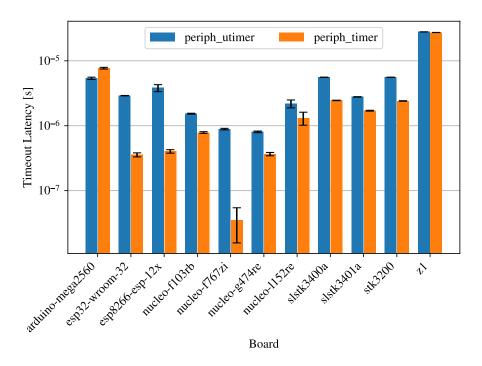

| 7.9          | Latencies of 1 ms timeouts at the platform-default timer frequency                                                              | 84            |

| 7.10         | Definition of the periodic timeout latency benchmark                                                                            | 86            |

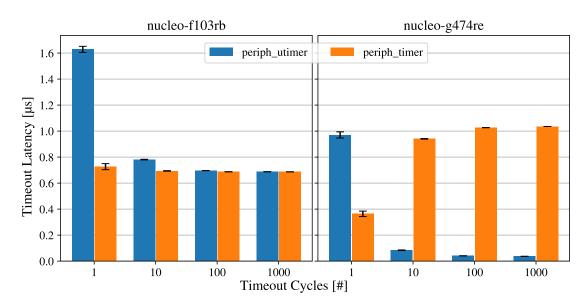

| 7.11         | Latencies of periodic 1 ms timeouts after different numbers of timeout cycles                                                   | 87            |

| 7.12         | Definition of the parallel callbacks benchmark                                                                                  | 88            |

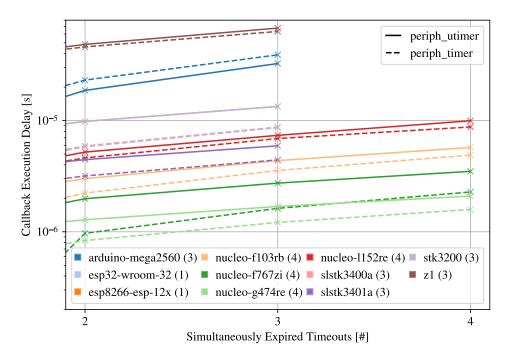

| 7.13         | Delay of compare match callback execution with simultaneously expiring timeouts                                                 | 89            |

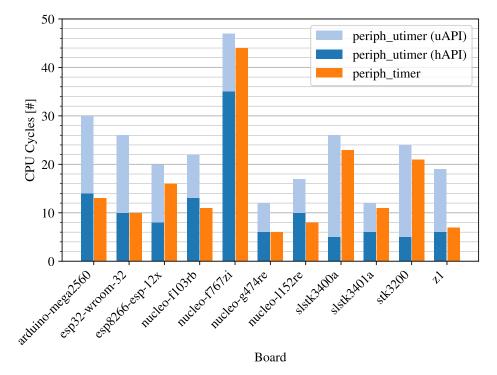

| 7.14         | CPU cycles consumed by NOP calls via APIs with different degrees of abstraction                                                 | 91            |

| 7.15         | Screenshot of a HiL unit test report                                                                                            | 98            |

# List of Tables

| 4.1  | Comparison of current low-level timer modules in RIOT OS                                    | 19  |

|------|---------------------------------------------------------------------------------------------|-----|

| 4.2  | Summary of device families we analyzed within our hardware-platform analysis .              | 23  |

| 4.3  | Hardware analysis results across all MCU platforms                                          | 26  |

| 6.1  | Total number of boards with uTimer implementations                                          | 63  |

| 7.1  | Overview of evaluated microcontroller boards                                                | 71  |

| 7.2  | Overview of hardware timers on the evaluated microcontroller boards $\ldots \ldots$         | 71  |

| 7.3  | Exposure of timer peripherals and channels                                                  | 95  |

| 7.4  | Timeout latencies and timeout error with unsupported parameters $\ldots \ldots \ldots$      | 97  |

| A.1  | Timer Comparison Matrix: STMicroelectronics STM32                                           | 113 |

| A.2  | Timer Comparison Matrix: Microchip / Atmel megaAVR                                          | 114 |

| A.3  | Timer Comparison Matrix: Microchip PIC32MX/MZ                                               | 114 |

| A.4  | Timer Comparison Matrix: Microchip / Atmel SAM3                                             | 114 |

| A.5  | Timer Comparison Matrix: Microchip / Atmel SAMD21                                           | 115 |

| A.6  | Timer Comparison Matrix: Espressif ESP8266                                                  | 115 |

| A.7  | Timer Comparison Matrix: Espressif ESP32                                                    | 115 |

| A.8  | Timer Comparison Matrix: Silicon Labs EFM32/EFR32                                           | 116 |

| A.9  | Timer Comparison Matrix: Silicon Labs EZR32                                                 | 116 |

| A.10 | Timer Comparison Matrix: Texas Instruments CC13x2 / CC26x2                                  | 117 |

| A.11 | Timer Comparison Matrix: Texas Instruments CC2538                                           | 117 |

| A.12 | Timer Comparison Matrix: Texas Instruments CC430                                            | 118 |

| A.13 | Timer Comparison Matrix: Texas Instruments LM4F120                                          | 118 |

| A.14 | Timer Comparison Matrix: Texas Instruments MSP430x1xx / MSP430x2xx                          | 118 |

| A.15 | Timer Comparison Matrix: Nordic Semiconductor nRF51x/52x                                    | 119 |

| A.16 | Timer Comparison Matrix: SiFive FE310-Gx                                                    | 119 |

| A.17 | Timer Comparison Matrix: NXP Semiconductors Kinetis                                         | 119 |

| A.18 | Timer Comparison Matrix: NXP Semiconductors LPC176x/5x $\hfill \ldots \ldots \ldots \ldots$ | 120 |

| A.19 | Timer Comparison Matrix: NXP Semiconductors LPC2387                                         | 120 |

# List of Acronyms

| <b>API</b> Application Programming Interface.              |

|------------------------------------------------------------|

| <b>BLE</b> Bluetooth Low Energy.                           |

| <b>CAN</b> Controller Area Network.                        |

| <b>CI</b> Continuous Integration.                          |

| CLK Clock.                                                 |

| <b>CMP</b> Compare Match.                                  |

| <b>CoAP</b> Constrained Application Protocol.              |

| <b>CPU</b> Central Processing Unit.                        |

| <b>DHCP</b> Dynamic Host Configuration Protocol.           |

| <b>DMA</b> Direct Memory Access.                           |

| <b>DUT</b> Device Under Test.                              |

| $\textbf{GPIO} \ \ \textbf{General-purpose input/output}.$ |

| <b>HAL</b> Hardware Abstraction Layer.                     |

| <b>hAPI</b> Hardware-facing API.                           |

| <b>HiL</b> Hardware in the Loop.                           |

| <b>INT</b> Interrupt.                                      |

| <b>IoT</b> Internet of Things.                             |

| <b>IPv6</b> Internet Protocol version 6.                   |

- **IRQ** Interrupt Request.

- **ISR** Interrupt Service Routine.

LoRaWAN Long Range Wide Area Network.

- $\ensuremath{\mathsf{LSB}}$  Least Significant Bit.

- MCU Microcontroller Unit.

- **MQTT** Message Queuing Telemetry Transport.

- $\ensuremath{\mathsf{MSB}}$  Most Significant Bit.

- ${\bf NOP}\,$  No Operation.

- **OS** Operating System.

**OVF** Overflow.

**PHiLIP** Primitive Hardware in the Loop Integration Product.

**PLL** Phase-locked Loop.

$\ensuremath{\mathsf{PWM}}$  Pulse-width Modulation.

$\ensuremath{\mathsf{RAM}}$  Random-access Memory.

**RF** Robot Framework.

- **ROM** Read-only Memory.

- **RPL** Routing Protocol for Low-Power and Lossy Networks.

${\sf RTC}\,$  Real-time clock.

- ${\sf RTOS}\,$  Real-time Operating System.

- **SDK** Software Development Kit.

- **SDLC** Systems Development Life Cycle.

${\bf SoC}\,$  System on a Chip.

**TCM** Timer Comparison Matrix.

- $\ensuremath{\mathsf{TCP}}$  Transmission Control Protocol.

- **uAPI** User-facing API.

- ${\sf UART}\,$  Universal Asynchronous Receiver-Transmitter.

- ${\boldsymbol{\mathsf{UDP}}}$  User Datagram Protocol.

- $\boldsymbol{\mathsf{WDG}}$  Watchdog Timer.

- **WSN** Wireless Sensor Network.

# List of Symbols

| Symbol     | Notation                  | Description                                               |

|------------|---------------------------|-----------------------------------------------------------|

| $D_{cb}$   | Callback Execution Delay  | Time between timeout expiry and user-callback execution   |

| $J_{cb}$   | Callback Execution Jitter | Standard deviation of $D_{cb}$                            |

| f          | Frequency                 | Number of timer cycles per second                         |

| $O_{GPIO}$ | GPIO Overhead             | Time required to signal start and stop of a measurement   |

| p          | Padding                   | Number of bytes for aligning data within memory           |

| 8          | Size                      | Number of bytes required for storing a data block         |

| σ          | Standard Deviation        | Statistical measure for the dispersion of data            |

| au         | Timeout                   | Length of a timeout period                                |

| $E_{\tau}$ | Timeout Error             | $L_{\tau}$ in proportion to the time<br>out length $\tau$ |

| $J_{\tau}$ | Timeout Jitter            | Standard deviation of $L_{\tau}$                          |

| $L_{\tau}$ | Timeout Latency           | Difference between expected and actual end of a timeout   |

# List of Listings

| 1  | Excerpt of the utim_periph_t struct                                                                        | 43  |

|----|------------------------------------------------------------------------------------------------------------|-----|

| 2  | Excerpt of the utim_driver_t struct                                                                        | 44  |

| 3  | Excerpt of the dynamic property interface that is provided by the hAPI $\ldots$ .                          | 45  |

| 4  | Code Example: Platform-independent use of a single timer                                                   | 53  |

| 5  | Code Example: Interchangeable use of different timer types $\ldots \ldots \ldots \ldots$                   | 53  |

| 6  | Encoding of channel-specific properties within utim_prop_t                                                 | 61  |

| 7  | Creation of regular and virtual timer instances                                                            | 66  |

| '  |                                                                                                            | 00  |

| 8  | Disassembly of the timer_read() function (NOP version)                                                     | 90  |

| 9  | Definition of the internal device identifier type utim_tt                                                  | 121 |

| 10 | Definition of the utim_periph_t struct                                                                     | 122 |

| 11 | Default definition of the counter value type utim_cnt_tt.                                                  | 122 |

| 12 | Definition of enumeration types for timer properties: utim_clk_t, utim                                     |     |

|    | <pre>mode_t, utim_chan_mode_t, utim_cnt_dir_t</pre>                                                        | 123 |

| 13 | Definition of the hAPI property interface types and their encoding                                         | 124 |

| 14 | Definition of timer callback function signatures and ISR contexts                                          | 125 |

| 15 | Definition of the utim_driver_t struct                                                                     | 126 |

| 16 | Definition of the hAPI function: init()                                                                    | 127 |

| 17 | Definition of the hAPI function: get_property()                                                            | 127 |

| 18 | Definition of the hAPI function: set_property()                                                            | 128 |

| 19 | Definition of the hAPI function: enable()                                                                  | 128 |

| 20 | Definition of the hAPI function: read()                                                                    | 128 |

| 21 | Definition of the hAPI function: write()                                                                   | 129 |

| 22 | Definition of the hAPI function: set_channel()                                                             | 129 |

| 23 | $Definition \ of \ the \ optional \ hAPI \ function: \ \texttt{is\_valid\_freq()}  \ldots  \ldots  \ldots$ | 130 |

| 24 | Definition of the uAPI function: utimer_get_periph()                                                       | 131 |

| 25 | Definition of the uAPI function: utimer_init()                                                             | 131 |

| 26 | Definition of the uAPI function: utimer_start()                                                            | 132 |

| 27 | Definition of the uAPI function: utimer_stop()                                                             | 132 |

| 28 | Definition of the uAPI function: utimer_read()                                                             | 132 |

| 29 | Definition of the uAPI function: utimer_write()                                                     | 133 |

|----|-----------------------------------------------------------------------------------------------------|-----|

| 30 | Definition of the uAPI function: utimer_set()                                                       | 133 |

| 31 | Definition of the uAPI function: utimer_set_absolute()                                              | 134 |

| 32 | Definition of the uAPI function: <code>utimer_set_periodic()</code>                                 | 134 |

| 33 | Definition of the uAPI function: utimer_clear()                                                     | 135 |

| 34 | Definition of the uAPI function: <code>utimer_get_property()</code>                                 | 136 |

| 35 | Definition of the uAPI function: <code>utimer_set_property()</code>                                 | 136 |

| 36 | $Definition \ of \ the \ optional \ uAPI \ function: \ \texttt{utimer_is_valid_freq()} \ . \ . \ .$ | 137 |

| 37 | Definition of the optional uAPI function: utimer_get_nearest_freq()                                 | 137 |

# 1 Introduction

With the ubiquitous Internet of Things (IoT), applications and deployment contexts of embedded systems vastly increased in number and heterogeneity. Devices are often severely constrained in terms of computational power, memory, and energy consumption. Hardware manufacturers respond to this by continuously improving their microcontroller units (MCUs), including CPUs and on-board peripherals. Timers in particular are required by almost every application and have great influence on the total energy consumption, wherefore an ever-increasing variety of them exists. Firmware developers must adapt to this frequent changes in hardware accordingly. Embedded operating systems conveniently abstract from the underlying hardware and therefore became the prevalent solution for developing sustainable applications in the IoT. They are expected to provide portable yet feature-rich hardware interfaces, carefully weighing generalization against its inevitable performance degradation. However, current operating systems struggle in doing so due to their inflexible APIs and the high heterogeneity of target devices. Their long unchanged function definitions are limited to basic timer features, hence prevent exposure of advanced timer features and innovative timer types. The need for sound and flexible low-level peripheral abstraction therefore arises to meet the requirements of embedded applications.

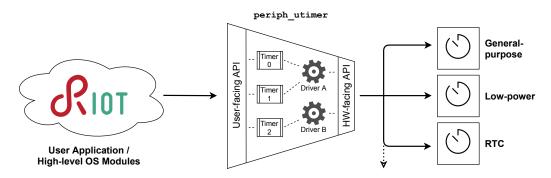

RIOT [3] is an increasingly popular open-source operating system that targets low-power and resource constrained devices in the IoT and Wireless Sensor Networks. It provides five distinct low-level timer APIs, distinguished by exposed timer types and features. We aspire to unify the existing modules into a single streamlined interface. It shall comprehensively present novel hardware timers including all their functions, while preserving application portability. Our goal is not to provide a fully-featured and ready-to-use implementation, but rather a sound and future-proof low-level timer API design. The major contributions of this work are therefore primarily of analytical and conceptual nature. We give profound insight into the variety of hardware timers and how they are used within embedded applications, to base a reliable API design on. Since RIOT targets more than 200 MCU boards, a solid interface must not only be able to expose this hardware diversity, but the numerous device-specific drivers must likewise perform correctly and resource efficiently. Automated cross-platform unit tests and performance benchmarks encourage the development of sustainable implementations and permit their sound evaluation. The contributions of our work are highlighted in the remainder of this section.

#### 1 Introduction

Chapter 2 introduces fundamental concepts and techniques that are encountered throughout this thesis. It explains the basic components that make up a hardware timer and how they interact with each other. Abstraction of on-board MCU peripherals and embedded operating systems are moreover highlighted. The manifold challenges that arise when designing platform-independent hardware interfaces for a heterogeneous range of devices are outlined in our problem statement in Chapter 3. We address the limits of platform-specific solutions and the difficulties that come with platform-agnostic ones. Hardware diversity, functional validation, and performance optimization are likewise discussed.

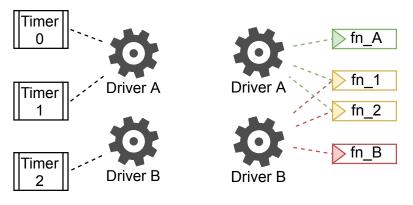

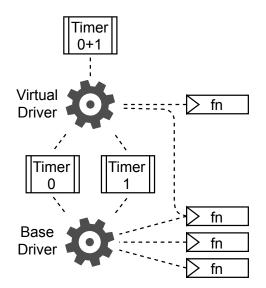

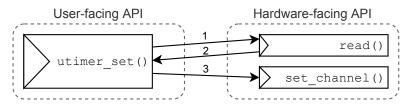

In Chapter 4, a total of four analyses are conducted. First, a review of related work on low-level timer properties, hardware abstraction techniques, and timer modules of embedded operating systems is performed. The demands of high-level timer subsystems for peripheral interfaces are furthermore highlighted. Second, we take a closer look at the current low-level timer APIs of RIOT, identifying similarities and potential shortcomings. Third, we contribute a large-scale analysis of all timer peripherals that are found on RIOT supported boards. Results from those 43 MCU families are compiled into a comprehensive overview and discussed in a comparative fashion. Fourth, timing requirements of IoT applications are determined by examining timer usage within the whole RIOT code base as well as prevalent network communication protocols. We use the insights from all four analyses within Chapter 5 to base the design of our low-level timer API on them. The proposed *uTimer* API consists of two distinct layers that allow transparently interchangeable use of all available timer peripherals, provide out-of-the-box support for both generic and device-specific functions, and preserve platform-independence whenever possible. Besides the design itself, we discuss its trade-offs and remaining issues. Within Chapter 6, uTimer is implemented for six distinct microcontroller platforms, covering a total of 129 boards. We describe both its generic and platform-specific components, as well as their integration into the RIOT system architecture. The correct behavior of implementations is subsequently verified by timer unit test suites across all platforms.

Our design is evaluated within Chapter 7. Extensive benchmark suites are developed to assess the manifold aspects of low-level timer drivers in an automated fashion. The performance of uTimer is compared to existing APIs on 14 different MCUs. We reveal the impact of individual design decisions and isolate the overhead that is inherent to the APIs themselves. This is followed by an evaluation of various qualitative aspects and the suitability for integration into high-level timer subsystems. The impact of the contributed benchmark suites on the operating systems development life cycle is furthermore discussed there. Chapter 8 then closes this thesis with a concluding summary of our contributions and gives an outlook on future work.

# 2 Background

This chapter introduces basic concepts and techniques that are used in this thesis. Section 2.1 starts by explaining what microcontrollers are and how their basic timer peripherals work. It is followed by a description of hardware abstraction techniques in Section 2.2 and a definition of embedded operating systems, including their purpose and goals, Section 2.3. This chapter provides only an initial overview, as all aspects touched upon will be covered in detail within our extensive analysis Chapter 4.

# 2.1 Microcontrollers and Timer Peripherals

A microcontroller unit (MCU) is an integrated circuit often found in embedded systems. It combines a central processing unit (CPU), integrated memory, and peripheral devices within a single chip package. In addition to system memory, it typically likewise includes read-only memory (ROM) and random-access memory (RAM). Clock generators and internal oscillators are moreover found in most devices. Today, a broad spectrum of MCUs is offered to cover a wide range of possible applications. These differ in terms of computing power, energy consumption, and on-board peripherals.

Among the manifold peripherals that are available, hardware timers are one of the few that are essential to all embedded devices [29]. They are used to measure time and generate periodic signals independent of the main program flow. The CPU hereby can primarily execute the deployed firmware and is only rarely interrupted for timekeeping tasks. This is indispensable for most embedded applications. Hardware timers, also referred to as *low-level timers*, differ from software timers in that they are always physical hardware modules and are not generated by the device firmware based on a purely virtual clock source.

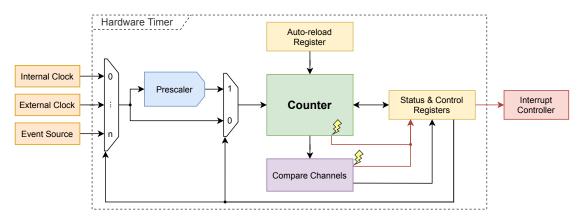

Components of a basic timer peripheral are illustrated in Figure 2.1. Hardware timers count pulses of an independent clock or external events within an internal counter register. It is either incremented or decremented at a fixed frequency until a threshold is reached. This can either be the maximum counter width or an arbitrary value, specified within a designated auto-reload register. Once reached, the counter value is reset, an overflow is signalled, and the timer may continue to count. Compare channels allow measuring time by triggering system events, whenever the counter register reaches a certain value. They hereby request the CPU to interrupt the main program flow, enabling user applications to asynchronously react to elapsed timeouts. Counting speed is determined by the selected timebase, i.e., clock source, and can be altered by a prescaler or phase-locked loop (PLL). All functions of a timer module can be configured through its control registers. Peripheral status is likewise exposed and includes various information, such as pending interrupts or current counting mode.

Figure 2.1: Core components and functional overview of a basic hardware timer. Interrupt event sources are indicated by flash symbols.

Today, various types of specialized hardware timers are offered alongside the ubiquitous generalpurpose modules described above. These include among others: high-speed timers, low-power timers, and real-time counters. Although each type possesses a distinct feature set, they all share the same basic concepts of operation. Firmware developers can therefore select the most suitable peripherals from a wide range of timers and use either solely its basic functions or also advanced timer-type specific features, whenever required for the current use case. In addition to the huge variety of on-board peripherals, external timekeeping devices<sup>1</sup> exist, but are used far less frequently. They become an attractive energy-saving solution whenever very long-running timeouts (> 10 s) are employed. Such external devices allow to completely power down the MCU during timeout periods and only consume ultra low currents (< 50 nA) themselves.

# 2.2 Hardware Abstraction Techniques

All hardware peripherals within MCUs are usually controlled via designated registers. Those registers are read to determine device status or to receive application data. Writing them allows to control and configure on-board devices or triggers specific hardware functions. Whenever accessing peripheral registers, the CPU must know their exact memory address and the firmware

<sup>&</sup>lt;sup>1</sup>For example, the Texas Instruments TPL5111 ultra low power system timer (35 nA) for power gating in duty cycled applications. See: https://www.ti.com/product/TPL5111 (Accessed: 04.01.2022)

developer must interpret bit values correctly. This direct form of register access is not only highly error-prone and cumbersome, but it also ties an application firmware to the target hardware. To aid this problem, hardware is abstracted by so-called hardware abstraction layers (HALs). They enable the user application to access hardware through a well-defined application programming interface (API). Device manufacturers always provide at least a basic register mapping, while some vendors even offer a rich function-based HAL. Register mappings are usually made available in the form of header files that contain preprocessor macros. These often define custom data types that in turn are used to model peripheral registers as well as complete peripheral devices. Function-based APIs are built on top of these mappings and are commonly shipped within vendor-specific software development kits (SDKs).

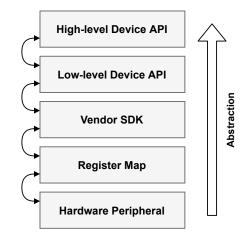

Besides such basic forms of hardware abstraction, there may be additional, more complex layers. In general, lower layers are hardware-dependent up to a certain point and higher layers do get increasingly independent of the underlying hardware while hiding more and more details of low-level implementations. Well-designed APIs make up the interfaces between two adjacent abstraction layers.

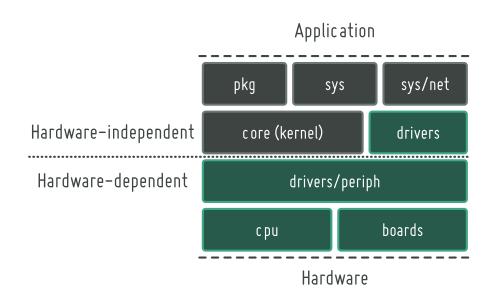

Figure 2.2: Example of a highly abstracted hardware peripheral. Each box represents one layer of abstraction.

An example of a multi-layered hardware abstraction is illustrated in Figure 2.2. Here, registers are first mapped to their memory addresses and peripherals are then exposed via a vendorprovided SDK. This SDK in turn is used by a low-level device API to provide the application with performant and user-friendly access to all peripheral features. Finally, a high-level device API eliminates hardware-dependence entirely and provides additional features that go beyond pure hardware presentation. User applications that exclusively use this high-level device API can be run on any target hardware that implements the low-level device API. However, this large amount of abstraction imposes a notable computational overhead and limits access to special hardware-specific features, which potentially makes the API unsuitable for some applications.

# 2.3 Embedded Operating Systems

Operating systems (OSs) are collections of reusable software components that interface device hardware, manage system resources, and provide basic services to user applications. Embedded OSs make up a subset of these and are designed to run on resource constrained hardware. The targeted devices can be limited in multiple aspects, including processing speed, system memory, and allowed power consumption [31]. Operating systems for embedded devices therefore place a strong emphasis on resource efficiency and offer only a very limited set of features compared to general-purpose operating systems. Developers are relieved from repeatedly implementing hardware-specific driver code and provided with extensively tested solutions to common software problems. These typically include memory management, task scheduling, or hardware abstraction and are complemented with implementations for various communication protocols. Application code can often be written in a portable and platform-agnostic fashion, allowing for quick changes in target hardware. Embedded OSs hereby greatly reduce time-to-market and can improve code quality. The application and the operating system are usually statically linked together into a single firmware binary, effectively limiting the system to run only a single application. As a consequence, the OS generally dictates the set of usable programming languages, as for example the nesC dialect used for writing TinyOS [56] application.

There is a wide variety of application-specific operating systems, of which real-time operating systems (RTOSs), such as QNX [8] or FreeRTOS [6], are by far the prevalent type. However, a sharp distinction between different OS types is not always possible, as nowadays most embedded OSs fall into several categories. RIOT [3], for example, is an open-source OS specifically designed for resource constrained devices in the Internet of Things. It offers real-time capabilities and implements full multi-threading. The microkernel architecture of RIOT allows out-of-the-box support for a comprehensive list of features while keeping the minimum memory requirements low. User applications can be written in the C, C++, or Rust programming languages. We will go into detail about various aspects of the RIOT operating system throughout the body of this work.

# **3** Problem Statement

The challenges with designing extensive yet flexible application programming interfaces for a broad and heterogeneous spectrum of target devices are manifold. In this chapter we describe the different aspects to this problem with a focus on timer peripherals.

Hardware timers are part of every microcontroller and essential to almost all applications. Due to their vast use cases, they affect numerous aspects of embedded systems [29]. These include energy consumption, responsiveness, data transmission, and system performance in general. With the tight resource constrains that are put upon devices within the Internet of Things or Wireless Sensor Networks, their comprehensive yet efficient use is of utmost importance [17]. Although developing hardware APIs may seem simple at first, it quickly becomes challenging when different types of peripherals shall be exposed via a uniform interface [22]. Because of the far-reaching influence of timer peripherals, we nevertheless consider it essential to address this problem in a sound manner. Updating nowadays outdated and insufficient APIs to support advanced timer features and optimizing low-level driver implementations brings numerous benefits for modern embedded applications.

# 3.1 Limits of Platform-specific Solutions

Hardware APIs present peripherals to user applications and other system modules in a convenient and user-friendly way. Whenever only a single peripheral needs to be exposed, the associated software interface can be easily tailored to it. Truly platform-specific solutions do not distinguish between different types within a single class of peripherals, such as basic and advanced timers. This approach is perfectly sufficient, as long as only a single microcontroller is targeted and future application portability is no concern. API design, however, quickly becomes challenging when multiple yet still mostly homogeneous devices, e.g., MCUs of the same family, are targeted. Even though their peripherals are almost identical in operation principles and features, some may require a slightly modified driver or do not support a specific feature. With a large and highly heterogeneous range of target devices, this problem intensifies and can no longer be solved by any platform-specific solution. In such cases, differentiating between target platforms within low-level peripheral layers becomes inevitable [3]. Well-designed hardware APIs nonetheless should bundle peripherals of the same class behind a single interface. Fully platform-specific solutions struggle at implementing this due to their inflexibility and lack of abstraction. Platform-agnostic APIs instead are capable of modeling these peripheral differences. They achieve this by providing multiple implementation variants that possess a common interface. Whenever the target device is changed, the respective driver for the new device is automatically loaded. Since all drivers share the same interface, user applications remain fully compatible and therefore do not need to be manually modified. This approach, however, tends to limit available functions to the basic set of features that is common to all target devices [30]. While this potentially results in simple and streamlined application programming interfaces, features that are only supported by a subset of the platforms are hereby often left unexposed. With growing peripheral diversity, this not only increasingly limits the power of the API, but also prevents most optimization opportunities that MCUs nowadays offer.

Embedded operating systems are designed to provide a sound base that user applications can build upon [3]. They support a large range of devices and allow for application portability to a certain extent. Fully platform-specific hardware APIs therefore are generally considered unsuitable for embedded OSs.

# 3.2 The Abstraction Trade-off

In the previous section we pointed out that an increase in application portability, i.e., platform compatibility, is usually linked to an increase in abstraction. However, each additional software layer entails further computational and memory overhead [22]. Containing the computational overhead is particularly important with timekeeping applications in order to maintain timeout accuracy and to ensure overall system responsiveness. The effects on memory consumption, on the other hand, are less important, but also not to be neglected [51].

This means that operating system developers must carefully weigh the benefits and drawbacks of different API designs. Forcing user applications and OS modules to directly interact with timer hardware registers may yield near-optimal performance but is highly error-prone, laborious, and prevents portability. Abstracting timer peripherals results in portable and user-friendly solutions but decreases performance. Hence, choosing an appropriate level of abstraction can be challenging and is referred to as the *abstraction trade-off* [55]. Sacrificing system memory to reduce computational complexity can alleviate the negative performance impact to a certain extent. Corresponding techniques include, for example, replacing resource-heavy calculations with lookup tables and loop unrolling. This idea was first described by Hellman [24] and is referred to as the *time-memory trade-off* 1.

<sup>&</sup>lt;sup>1</sup>The time-memory trade-off is also referred to as the space-time trade-off.

Resource requirements of embedded systems are also important from an economic point of view. Here, the challenge lies in balancing production and development costs. An increased resource consumption may require to upgrade the target hardware. This can lead to significant increases in production costs, as embedded devices are often deployed in large quantities. Complete renunciation of abstraction, on the other hand, skyrockets firmware development costs, dramatically increases time-to-market, and is therefore also undesirable [31].

Next to pure performance aspects stand the capabilities of an API. The more abstraction is applied, on one hand, the more details of the underlying hardware are hidden [22]. With little to no abstraction, on the other hand, solutions fail to support heterogeneous target devices. The current peripheral APIs of embedded OSs therefore tend to be limited to generic features, leaving progressive but device-specific ones unexposed, as confirmed by our review of timer APIs in Section 4.1.4. In order to comprehensively support novel timers while sacrificing neither portability nor compatibility, a careful balance between feature support and generalization must be obtained. The need for modern low-level timer APIs that supersede the existing rigid and functionally limited interfaces therefore arises.

So the problem of abstracting timer hardware lies in carefully balancing the manifold aspects of the outlined trade-offs. A low-level timer API should offer feature-rich and convenient timer use while confining performance degradation and allowing for comprehensive application portability at the same time.

# 3.3 Hardware Heterogeneity

The great diversity of embedded systems makes the development of generic solutions extremely difficult [31]. With respect to hardware timers, characteristics and features of general-purpose peripherals are well-known and allow for sound generalization. Advanced timer types, on the other hand, differ largely between device families in both capabilities and features.

Hardware manufacturers continuously improve existing peripherals and present new timer types to satisfy the demanding requirements of modern embedded applications. The RIOT OS alone supports more than 200 different microcontroller boards, consisting of 43 device families from eight manufacturers, and new devices steadily expand this range as they become available [48]. Each additional board potentially introduces novel types of timer peripherals. A comprehensive overview of the properties and capabilities of the target hardware does not exist. However, profound knowledge about it is a necessity for designing extensive yet lasting APIs. Accordingly, it is becoming increasingly difficult for OS developers to design streamlined software interfaces that are also able to support the latest hardware features.

# 3.4 Validation and Optimization

Besides all above discussed aspects, long-term system operability and component availability are likewise important parts of the life cycle of embedded systems [31]. Sound application portability allows for effortless changes in target hardware whenever the current microcontroller is no longer manufactured or cheaper devices become available. This challenges embedded operating systems by expecting user applications to behave identical on all supported devices. In addition, extensive regression testing must be performed to ensure that neither upcoming nor recent changes to the OS codebase cause bugs or major performance degradation within existing implementations.

Unit tests support developers by verifying proper behavior of system modules and low-level code on both new and currently supported devices. With RIOT OS, for example, extensive test suites already assert the functionality of low-level timer drivers. Their periodic execution on a subset of all supported boards greatly reduces the risk of malfunctioning or even fully dysfunctional implementations [58]. Benchmarks that additionally assess the performance of low-level drivers, however, are not yet available [28]. This makes quantifying the impact of software design decisions and pending pull requests on non-functional requirements impossible. Whether or not a certain microcontroller fulfills application requirements therefore cannot easily be determined. The lack of benchmarks not only hinders the development of performant peripheral drivers, but potentially also leaves side effects of imminent code changes undetected. This problem again intensifies with the steadily increasing number of targeted boards. Automated and periodic execution of qualified benchmark suites therefore is almost inevitable for providing reliable and lasting embedded OSs for a constantly evolving spectrum of embedded devices [3].

# 4 Analysis

A well-founded overview of both hardware and software is essential for creating a knowledge base that ensures a viable and future-proof API design. We therefore conduct four different analyses prior to designing the aspired low-level timer interface, as describe in Chapter 5.

This chapter starts with a survey of related work and embedded operating systems, which are frequently used with resource-constrained IoT devices, in Section 4.1. The timer subsystem of RIOT OS is separately discussed in detail within Section 4.2. Comprehensive insight into the diverse spectrum of timer peripherals is given by our large-scale hardware analysis in Section 4.3. Timer usage within the whole RIOT codebase is examined and findings are extended by timing requirements of network communication protocols in Section 4.4. Each section is individually concluded with a summary of its most important aspects.

# 4.1 Related Work

Scientific research related to embedded timer peripherals and their associated hardware APIs is presented in this section. It is split into the following four categories:

- a) characteristics of timer peripherals from a hardware point-of-view,

- b) comparative analyses of timer hardware across different MCUs,

- c) generic design aspects and implementation techniques for timer subsystems,

- d) properties, similarities, and issues of timer APIs found in popular embedded OSs for resource-constrained devices.

The listed publications were selected according to their anticipated relevance for this work, as estimated to the best of our knowledge.

# 4.1.1 Properties of Hardware Timers

Common operation principles of general-purpose timers, their basic feature set, and their typical characteristics are described by Kamal [29, pp. 152 - 159]. The author elaborates on available operation and counting modes, different peripheral states, and various timer properties. These

include, among others, counter register width, clock prescaling capability, and auto-reload functionality. We likewise cover these aspects within our analysis of timer hardware, as described in Section 4.3. Common use cases and exemplary applications for general-purpose timers are further depicted. These include measurement of time periods, task scheduling, and baud rate control for communication protocols. Moreover, other types of timing hardware, here namely real-time clocks (RTCs) and watchdog timers (WDGs), are briefly illustrated.

While less detailed than Kamal [29] did, Susnea and Mitescu [54] also give insight into generalpurpose timer peripherals. Their book extends the above publication by describing functions and operation principles of timer hardware that is capable of generating pulse-width modulation (PWM) output signals. The authors furthermore identify compare channels as another key component of timer peripherals that we therefore also incorporated into our hardware analysis.

Besides on-board peripherals, Dimitrievski *et al.* [17] highlight the huge energy-saving potentials of external ultra-low power timers. They harness a Texas Instruments TPL511, which consumes less than 35 nA and provides an accuracy of 1%. Battery lifetime of an IoT sensor node, deployed within a Wireless Sensor Network (WSN), could hereby be extended by a factor of up to 80. This not only shows the importance of energy preservation with resource restricted devices in general, but also showcases the tremendous optimization potential timer peripherals offer.

Reverter [47] uses a hardware timer to autonomously trigger peripheral actions independent of the CPU. This reduces the total number of wake-ups, resulting in a halving of the systems power consumption. He moreover found wake-ups to entail a significant overhead power consumption<sup>1</sup>. Driver support for hardware features that allow to maintain CPU sleep, such as auto-reload or timer chaining, therefore is of utmost importance with resource constrained devices.

## 4.1.2 Comparative Analyses of Timer Peripherals

Susnea and Mitescu [54, pp. 67-68, pp. 87-89] conducted a comparison of timer peripherals from three MCU families, namely Motorola HC11, Atmel AVR, and Intel 8051. They found that even though specific timer features differ, the assessed peripherals still share many common operation principles. Asynchronously waiting for a specified amount of time, measuring elapsed time, and counting of events are pointed out as predominant use cases. A low-level timer API, as we aspire it, must in particular be capable of the first two.

Sharp *et al.*, members of the TinyOS [56] developer community, compiled an overview of timer hardware during the specification of their timer interfaces. Timer properties of the Atmega128, the MSP430, and the Intel PXA27x MCUs are depicted within their TinyOS Enhancement Proposal #102 Appendix A [52, Ln. 676ff]. The authors found all three platforms to provide several

<sup>&</sup>lt;sup>1</sup>Overhead power consumption denotes the energy that is used just for transitioning between device power modes.

timer peripherals of at least two different types. Differences in counter width, clocking options, prescaler capabilities, and in the number of available compare channels were emphasized.

Further analyses of microcontroller hardware exist, but they do not cover timer peripherals at the required level of detail to derive interface design decisions from them. We therefore contribute a large-scale analysis of timer hardware ourselves in Section 4.3. It covers all the 43 device families that are supported by RIOT OS at the time of writing.

# 4.1.3 Hardware Abstraction and Timer Interfaces

The hardware abstraction layers (HALs) in RIOT are described by Baccelli *et al.* [3]. The OS provides a single peripheral layer that exposes hardware to system modules and user applications. This design keeps abstraction overhead low, but limits feature support.

The two-layered design by Kleeberger *et al.* [30] separates register access from peripheral driver code. This allows profound feature support and makes the abstract device drivers independent of the underlying hardware. The authors leverage this additional layer of abstraction to mock hardware peripherals during unit tests.

Handziski *et al.* [22] introduce another level of abstraction in their proposed HAL design. Each of its three layers allows for a different granularity of peripheral access. Hardware-independent APIs are provided, while access to platform-specific features is available at the cost of consciously sacrificing application portability. Developers are able to mix interfaces of different abstraction levels within the same firmware. The authors confirmed the feasibility of their multi-layered HAL by implementing it for a Wireless Sensor Network (WSN) application.

The Common Microcontroller Software Interface Standard (CMSIS) [2] is a widely used set of uniform APIs for Cortex-based devices, such as the extensive STM32 device family. It exposes core components, including the SysTick timer. Additional timer peripherals, however, remain unsupported by it, since these are not part of the generic Cortex processor family.

Another platform-independent but more extensive timer API is proposed by Lindgren *et al.* [35]. They assess similarities between timers of the STM32F4 and LPC1700 MCU families and discuss their impact on the proposed design. Common timer properties and features that can be exposed through a uniform API are identified. These include counter width, interrupt capability, prescalers, auto-reload, and compare channel count. The authors furthermore emphasize, that the exposure of multiple compare channels significantly benefits timer maintenance.

High-level timer modules heavily depend on low-level timer APIs and the underlying hardware abstraction layers. Even though these modules are beyond our scope, they provide important insight and allow the deviation of some implications for our aspired low-level timer API. A quick survey confirmed the statement of Lindgren *et al.* [35]: Access to multiple compare channels is

an indispensable requirement for many high-level timer modules [19], [25], [26], [43]. Most indeed do make beneficial use of timer features that go beyond the generation of a simple monotonic clock tick [13], [14], [19], [20], [25], [26]. With contemporary applications, driver support for low-power operation modes as well as dynamic clock and power management of peripherals are just as important [7], [41], [50].

## 4.1.4 Embedded Operating Systems

The timer subsystem of RIOT OS [4] consists of five low-level and two high-level timer modules. Due to its importance for our work, we present the provided features and discuss its different APIs separately and in-depth within Section 4.2.

Within this subsection, we inspect the timer APIs of four popular embedded operating systems that are likewise targeted at low-end embedded devices. More complex and sophisticated solutions, such as QNX [8] or Windows Embedded Compact [42], are not part of this survey. Each OS is discussed individually before a comparative summary concludes our findings.

### Contiki / Contiki-NG

Contiki [11] is a cross-platform embedded OS for low-power IoT devices. It is free to use and distributed under the terms of the 3-clause BSD license. While the original Contiki-OS received no updates since 2018, its successor Contiki-NG [12] is still under active development. Both possess a simple clock module that provides system time as an unsigned integer, representing clock ticks since system boot. Its API only allows to read the counter value and to actively wait for a number of clock ticks, hereby blocking the CPU. Based on this clock, five different timer APIs exist. Their interfaces and features are similar, but timer behavior and resolution differs.

The timer module offers high-resolution short-running timeouts, while stimer provides longrunning timeouts with one second resolution. Both require the application to actively poll for timer expiry but are safe to use within interrupt contexts. The etimer and ctimer modules can be used to either post an event to a process or to execute a callback function. Both, however, are not interrupt safe and operate with system tick resolution. Last, rtimer can use a separate clock instance to provide real-time task execution but might be unavailable when other OS modules are in use. None of the APIs allows direct access to available hardware timer peripherals, solely relying on software multiplexing timeouts onto the central system clock.

#### FreeRTOS

FreeRTOS [6] is a widely used real-time embedded OS that targets more than 40 MCU families and requires only 9 kBytes of ROM in its minimal configuration. It is actively developed by *Amazon Web Services* and released under the MIT license. The operating system itself only supports virtual software timers that are multiplexed onto a single system clock source. Application developers can extend it by manually writing platform-dependent code to make use of available hardware timers. This, however, closely couples the firmware to the current target hardware what impedes application portability. A single timer API is provided out-of-the-box, offering basic features, such as starting, stopping, deleting, and resetting timers. Each of its function calls exists in two variants that must be used according to the calling context. The API allows changing a timers period even after creation. A callback function can be attached to each timer and is executed by the timer service task upon timeout expiry. All virtual timers can furthermore be named and possess a unique identifier.

## TinyOS

TinyOS [34], [56] targets low-power MCUs, lays its focus on wireless communication, and therefore is commonly deployed within WSNs. Applications are written in the nesC dialect and are made up of multiple components that are connected via predefined interfaces. The OS can be used free of charge and is distributed under the terms of the BSD license. Its timer subsystem is described in the TinyOS Enhancement Proposal 102 [52]. All of its five timer APIs directly interface hardware peripherals. They, however, "do not attempt to capture [timer] diversity in a platform-independent fashion, [besides] measuring time and triggering events at specific times." [52, ln. 41ff]. Each interface is parameterized by its precision (e.g., 1 ms) and three additionally by their width (e.g., 32 bit), providing static properties of the underlying peripheral to the application.

Platforms expose their timers via the Counter and Alarm interfaces. The first only allows to read the current system time and signals overflows by a respective event. The Alarm interface extends the Counter interface by compare channels, signaling timeout expiry via designated events. It is split into basic commands, such as start(), stop(), or fired(), and an extended interface with commands for advanced use, such as startAt(), isRunning(), or getAlarmValue(). Synchronous delays using active waiting are available via the BusyWait interface and LocalTime provides a fixed 32-bit counter without overflow event handling. Last, the Timer interface again is split into a basic and an extended command set. It supports periodic timeouts and can therefore be used as a base clock for software timer multiplexing.

#### Zephyr

Among all reviewed operating systems, Zephyr [39] is the newest project. This real-time opensource OS is targeted at generic IoT devices and is actively developed by the Linux Foundation. It supports a diverse range of boards and is distributed under the Apache 2.0 license. All available hardware is modeled using a DeviceTree [16] data structure and system components can interactively be configured using Kconfig [36].